Микроконтролер Semicon Регулатор на напрежение IC чипове TPS62420DRCR SON10 Електронни компоненти BOM list service

Атрибути на продукта

| ТИП | ОПИСАНИЕ |

| Категория | Интегрални схеми (ИС) |

| произв | Texas Instruments |

| Серия | - |

| Пакет | Лента и макара (TR) Рязане на лента (CT) Digi-Reel® |

| SPQ | 3000T&R |

| Състояние на продукта | Активен |

| функция | Слизам |

| Изходна конфигурация | Положителен |

| Топология | Бък |

| Тип изход | Регулируема |

| Брой изходи | 2 |

| Входно напрежение (мин.) | 2,5 V |

| Входно напрежение (макс.) | 6V |

| Напрежение - изход (мин./фиксиран) | 0,6 V |

| Напрежение - изход (макс.) | 6V |

| Ток - Изход | 600mA, 1A |

| Честота - Превключване | 2,25MHz |

| Синхронен токоизправител | да |

| Работна температура | -40°C ~ 85°C (TA) |

| Тип монтаж | Повърхностен монтаж |

| Опаковка / Калъф | 10-VFDFN открита подложка |

| Пакет устройства на доставчика | 10-VSON (3x3) |

| Основен номер на продукта | TPS62420 |

Концепция на опаковката:

Тесен смисъл: Процесът на подреждане, закрепване и свързване на чипове и други елементи върху рамка или субстрат с помощта на филмова технология и техники за микропроизводство, водещ до терминали и фиксирането им чрез заливане с ковък изолиращ носител за образуване на цялостна триизмерна структура.

Най-общо казано: процес на свързване и фиксиране на пакет към субстрат, сглобяването му в цялостна система или електронно устройство и осигуряване на цялостната работа на цялата система.

Функции, постигнати чрез пакетиране на чипове.

1. прехвърляне на функции;2. предаване на верижни сигнали;3. осигуряване на средство за разсейване на топлината;4. структурна защита и опора.

Техническото ниво на опаковъчното инженерство.

Инженерингът на опаковките започва след направата на IC чипа и включва всички процеси преди IC чипът да бъде залепен и фиксиран, свързан помежду си, капсулован, запечатан и защитен, свързан към печатната платка и системата се сглобява до завършване на крайния продукт.

Първото ниво: известно още като опаковане на ниво чип, е процесът на фиксиране, свързване и защита на IC чипа към опаковъчния субстрат или водещата рамка, което го прави модулен (сглобен) компонент, който може лесно да бъде взет, транспортиран и свързан към следващото ниво на сглобяване.

Ниво 2: Процесът на комбиниране на няколко пакета от ниво 1 с други електронни компоненти за образуване на платка.Ниво 3: Процесът на комбиниране на няколко платки, сглобени от пакети, завършени на ниво 2, за формиране на компонент или подсистема на основната платка.

Ниво 4: Процесът на сглобяване на няколко подсистеми в цялостен електронен продукт.

В чип.Процесът на свързване на компоненти на интегрална схема върху чип е известен също като опаковане на нулево ниво, така че опаковъчният инженеринг също може да бъде разграничен от пет нива.

Класификация на пакетите:

1, според броя на IC чиповете в пакета: пакет с един чип (SCP) и пакет с множество чипове (MCP).

2, според разграничението на уплътнителния материал: полимерни материали (пластмаса) и керамика.

3, според режима на свързване на устройството и печатната платка: тип вмъкване на щифт (PTH) и тип повърхностен монтаж (SMT) 4, според формата на разпределение на щифта: едностранни щифтове, двустранни щифтове, четиристранни щифтове и долни щифтове.

SMT устройствата имат L-тип, J-тип и I-тип метални щифтове.

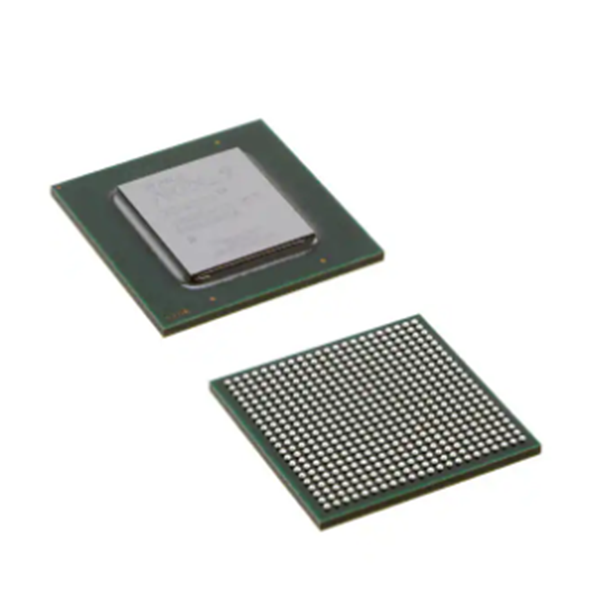

SIP: едноредов пакет SQP: миниатюризиран пакет MCP: пакет с метална гърне DIP: двуредов пакет CSP: пакет с размер на чипа QFP: четиристранен плосък пакет PGA: пакет с точкова матрица BGA: пакет с матрица с топка LCCC: безоловен керамичен носител на чип