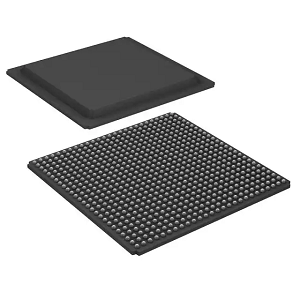

XC7Z030-2FFG676I – Интегрални схеми (IC), вградени, система върху чип (SoC)

Атрибути на продукта

| ТИП | ОПИСАНИЕ |

| Категория | Интегрални схеми (ИС) |

| произв | AMD |

| Серия | Zynq®-7000 |

| Пакет | поднос |

| Състояние на продукта | Активен |

| Архитектура | MCU, FPGA |

| Основен процесор | Dual ARM® Cortex®-A9 MPCore™ с CoreSight™ |

| Размер на светкавицата | - |

| Размер на RAM | 256KB |

| Периферни устройства | DMA |

| Свързаност | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Скорост | 800MHz |

| Основни атрибути | Kintex™-7 FPGA, 125K логически клетки |

| Работна температура | -40°C ~ 100°C (TJ) |

| Опаковка / Калъф | 676-BBGA, FCBGA |

| Пакет устройства на доставчика | 676-FCBGA (27x27) |

| Брой I/O | 130 |

| Основен номер на продукта | XC7Z030 |

Документи и медии

| ТИП РЕСУРСИ | ВРЪЗКА |

| Информационни листове | Zynq-7000 Всички програмируеми SoC преглед |

| Модули за продуктово обучение | Захранване на серия 7 Xilinx FPGA с решения на TI за управление на захранването |

| Информация за околната среда | Xiliinx RoHS сертификат |

| Представен продукт | Всички програмируеми Zynq®-7000 SoC |

| PCN дизайн/спецификация | Mult Dev Материал Промяна 16/декември 2019 г |

| Errata | Zynq-7000 Errata |

Екологични и експортни класификации

| АТРИБУТ | ОПИСАНИЕ |

| Състояние на RoHS | Съвместим с ROHS3 |

| Ниво на чувствителност към влага (MSL) | 4 (72 часа) |

| Състояние на REACH | REACH Незасегнати |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Приложен процесор (APU)

Основните характеристики на APU включват:

• Двуядрени или едноядрени ARM Cortex-A9 MPCores.Характеристиките, свързани с всяко ядро, включват:

• 2,5 DMIPS/MHz

• Работен честотен диапазон:

- Z-7007S/Z-7012S/Z-7014S (жична връзка): До 667 MHz (-1);766 MHz (-2)

- Z-7010/Z-7015/Z-7020 (жична връзка): До 667 MHz (-1);766 MHz (-2);866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (флип-чип): 667 MHz (-1);800 MHz (-2);1GHz (-3)

- Z-7100 (flip-chip): 667 MHz (-1);800 MHz (-2)

• Възможност за работа в режими с един процесор, симетричен двоен процесор и асиметричен двоен процесор

• Плаваща запетая с единична и двойна точност: до 2,0 MFLOPS/MHz всяка

• Механизъм за обработка на медии NEON за поддръжка на SIMD

• Thumb®-2 поддръжка за компресиране на код

• Кешове от ниво 1 (отделни инструкции и данни, по 32 KB всяка)

- 4-посочен набор-асоциативен

- Неблокиращ кеш на данни с поддръжка на до четири изключителни пропуска при четене и запис всеки

• Интегрирано устройство за управление на паметта (MMU)

• TrustZone® за работа в защитен режим

• Интерфейс на порта за кохерентност на ускорителя (ACP), позволяващ кохерентен достъп от PL до пространството на паметта на процесора

• Унифициран кеш от ниво 2 (512 KB)

• 8-посочен набор-асоциативен

• TrustZone активиран за сигурна работа

• Двупортова, вградена RAM памет (256 KB)

• Достъпен чрез CPU и програмируема логика (PL)

• Проектиран за достъп с ниска латентност от процесора

• 8-канален DMA

• Поддържа множество типове прехвърляне: от памет към памет, от памет към периферия, периферно устройство към памет и разпръснато събиране

• 64-битов AXI интерфейс, позволяващ високопроизводителни DMA трансфери

• 4 канала, посветени на PL

• TrustZone активиран за сигурна работа

• Интерфейсите за достъп с двоен регистър налагат разделение между сигурни и несигурни достъпи

• Прекъсвания и таймери

• Контролер за общо прекъсване (GIC)

• Три таймера за наблюдение (WDT) (по един на CPU и един системен WDT)

• Два тройни таймера/брояча (TTC)

• Поддръжка за отстраняване на грешки и проследяване на CoreSight за Cortex-A9

• Програмиране на макроклетка за проследяване (PTM) за инструкции и проследяване

• Cross trigger интерфейс (CTI), позволяващ хардуерни точки на прекъсване и тригери